BLUESPEC SYSTEMVERILOG FREE DOWNLOAD

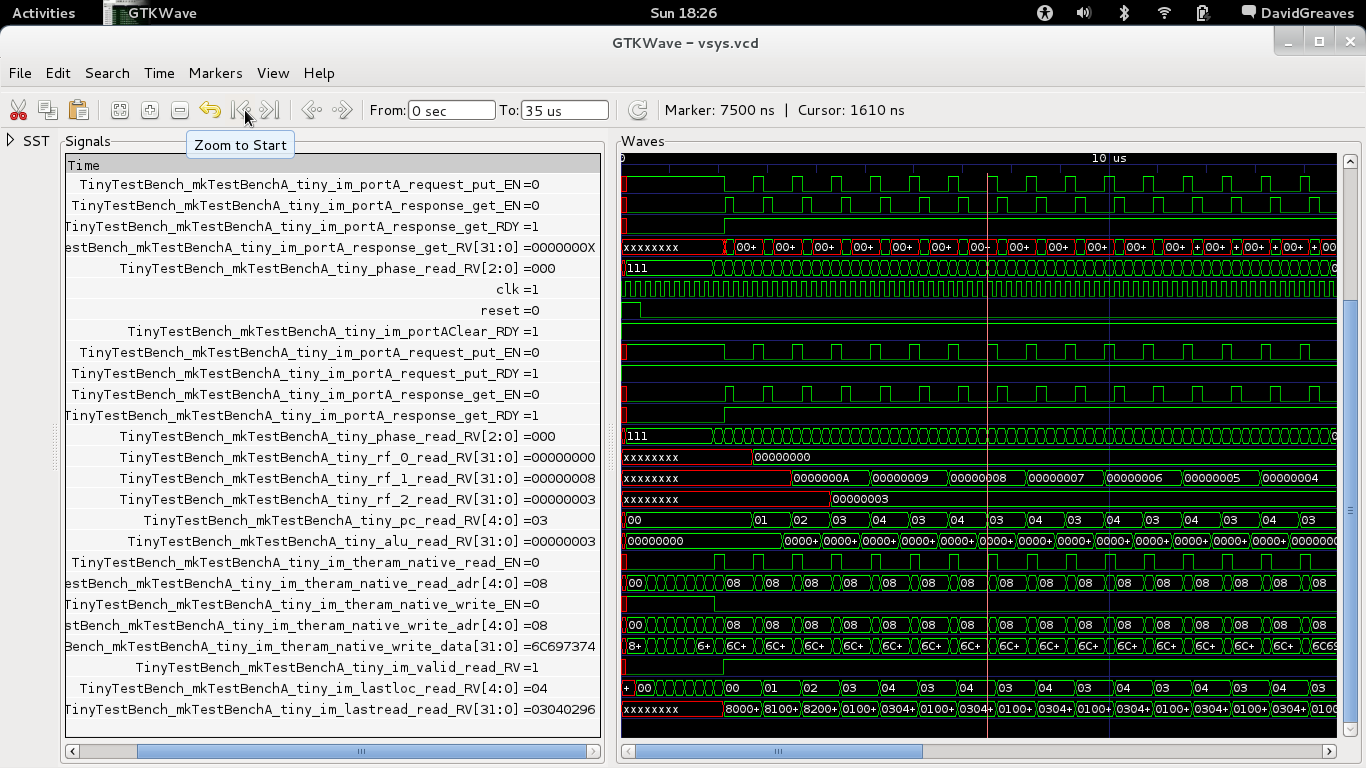

Rules also enable powerful reasoning about the functional correctness of systems. There may be hundreds. In BSV, "ready" and "enable" lines are automatically placed alongside anything carrying data. These are some of the seventy-four wire connections for mbxps. There are no rats-nests, and while modularisation is encouraged by the language, there's no pressure to create layer upon layer of wrapper modules just in order to set some generic parameters.

| Uploader: | Zolole |

| Date Added: | 20 July 2013 |

| File Size: | 44.83 Mb |

| Operating Systems: | Windows NT/2000/XP/2003/2003/7/8/10 MacOS 10/X |

| Downloads: | 17239 |

| Price: | Free* [*Free Regsitration Required] |

As a BSV novice, one of the first big differences I noticed was that BSV eliminated the characteristic problem of "over-modularisation", where the real implementation of some component is contained within many "wrapper" modules which add almost no functionality.

Simulation is extremely useful for debugging hardware components of any complexity. The obfuscation is unintentional but effective. For instance, modules can have a Client or Server interface - a two-way data channel complete with "ready" signals. There may be hundreds.

The memory bus is abstracted into the "BluetreeClient" sub-interface. It was not long before HDLs were being bluezpec to generate logic, both as photomasks used to etch designs onto silicon, and configurations for programmable devices.

The example below Verilog is typical: These are some of the seventy-four wire connections for mbxps.

BSV also treats modules, interfaces, rules, etc. There are plenty of predefined components such as FIFOs, RAMs and registers, which are extremely easy to use, and all bluepsec them are generic in that they can be used to contain any data type. The programmable devices were initially quite simple e. In other words, the concurrency model provided by rules is much more powerful and abstract than the low-level concurrency models provided by Verilog, VHDL and SystemC.

Bluespec - Wikipedia

So systemveriloy feature is useless for declaring data channels with "acknowledge" or "ready" signals, which are extremely common in real designs. This includes user-defined data types - BSV has "struct" and "enum", for example. If you do not have a HDL and simulator, you might well create ad-hoc simulators and modelling languages. Please contact Bluespec, Inc.

Jack Whitham - What's Good about Bluespec System Verilog

In many ways, both are equivalent. Rules also enable powerful reasoning about bluespecc functional correctness of systems. It extends the old HDLs in a sensible way, without imposing additional restrictions. The effect is to make it hard to understand the design, because the implementation is buried within layers of extremely verbose cruft. In BSV, an interface is composed of "methods" which may act as inputs or outputs and of sub-interfaces which may themselves contain methods and sub-interfaces.

They describe logic circuits. The "rats-nest" problem interacts horribly with the "over-modularisation" problem, because the rats-nest is repeated at each level of the hierarchy, systemverrilog if you want to add, remove or redefine a wire, then you have to do that everywhere.

VHDL allows you to define your own types, so you can have a special type for any interface that bundles multiple wires together. Systemferilog BSV, "ready" and "enable" lines are automatically placed alongside anything carrying data.

Jack Whitham

Within the Cortex-M0 module, we can reuse a cache module mkL1Cache and link it to the external "client" interface with a single line. You can find designs like this on Opencoresbut also from industrial engineers. During the last year, I have had the great privilege of using a relatively b,uespec hardware description language HDL named " Bluespec System Verilog ". On the subject of interfaces, a third benefit of BSV is that there is systemveripog rich set of predefined interface types to represent common ways to link components together.

VHDL has better support for different data types and "generic" parameterisable components, but it can be more difficult to read, because the verbosity means that there is a low signal-to-noise ratio.

VHDL is verbose while Verilog is terse. BSV even has a "state machine" module which makes it possible to write state machines as if they were programs. This automates the generation of control logic to manage complex concurrent state update, a major source of errors in current design methodology where this logic must be manually coded by the designer.

They can be described using less code, and with less potential for error.

Comments

Post a Comment